A hardware coprocessor instruction with no coprocessor present Palmerston North

Coprocessor Find link ARM’s developer website includes documentation, tutorials, support resources and more. Over the next few months we will be adding more developer resources and documentation for all the products and technologies that ARM provides.

US Patent for Coprocessor interface transferring multiple

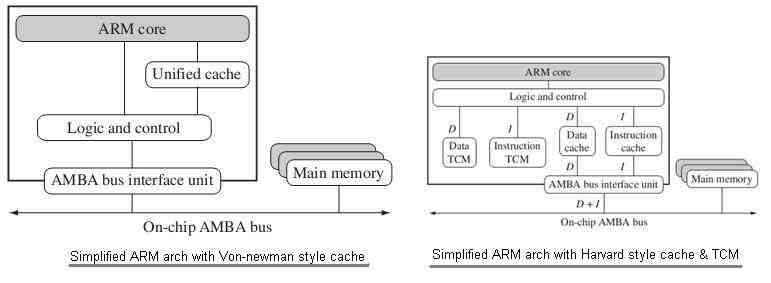

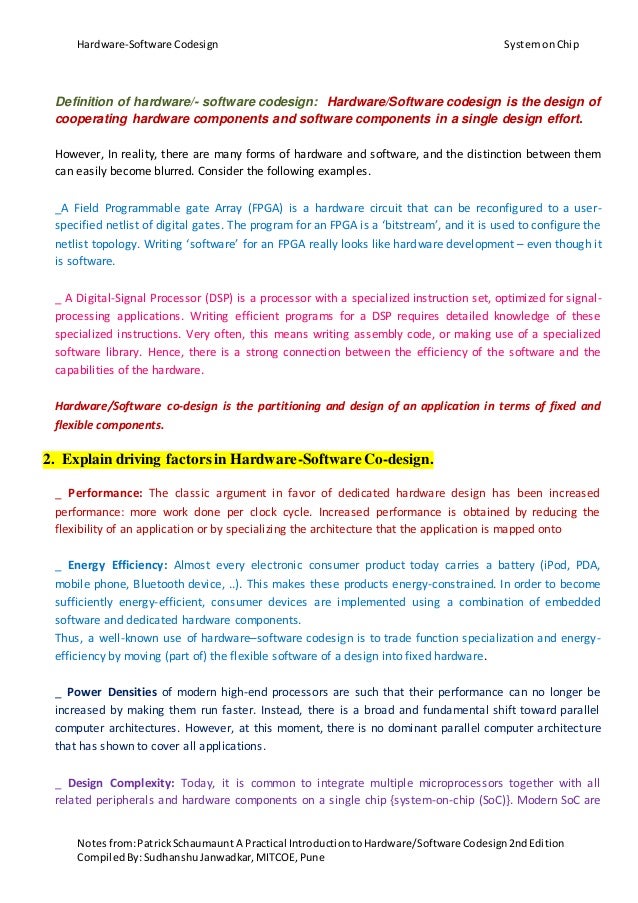

ARM7tdmi coprocessor datasheet & applicatoin notes. 41 Architectures of Flexible Symmetric Key Crypto Engines—A Survey: From Hardware Coprocessor to Multi-Crypto-Processor System on Chip LILIAN BOSSUET, University of Lyon MICHAEL GRAND, University of Bordeaux LUBOS GASPAR and VIKTOR FISCHER, University of Lyon GUY GOGNIAT, University of South Brittany Throughput, flexibility, and security form the design trilogy of reconfigurable crypto, 3.4 Instruction memory Request Control (IMEM REQ CNTRL) register eld we present a new SCU architecture that is based on a Xilinx Mi- SCU is a hybrid system that utilizes a hardware coprocessor to accelerate data stream processing. 1.1 Related Work Symbiote Coprocessor Unit (SCU) [4] is an FPGA-based coprocessor designed to.

Hardware-based encryption is the use of computer hardware to assist software, or sometimes replace software, in the process of data encryption.Typically, this is implemented as part of the processor's instruction set. For example, the AES encryption algorithm (a modern cipher) can be implemented using the AES instruction set on the ubiquitous x86 architecture. Find link is a tool written by Edward Betts.. Longer titles found: Apple motion coprocessors () searching for Coprocessor 238 found (425 total) alternate case: coprocessor Nintendo 64 technical specifications (2,091 words) exact match in snippet view article find links to …

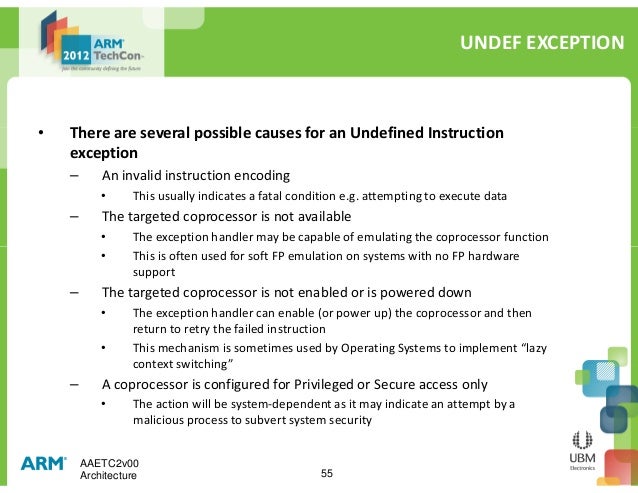

No. An 80487 would have been a math coprocessor for an 80486 general-purpose microprocessor...just like the 8087 was the math coprocessor for the 8086 and 8088, the 80287 for the 80286, and the 12/12/2012 · If the decode stage sees a coprocessor instruction, then it offers it to the relevant coprocessor. But if the coprocessor is not present or doesn't recognize the instruction, then the ARM takes an undefined instruction exception, which allows you to …

No. An 80487 would have been a math coprocessor for an 80486 general-purpose microprocessor...just like the 8087 was the math coprocessor for the 8086 and 8088, the 80287 for the 80286, and the The assembler tool comprises a set of commands which enable the central processor to manipulate the coprocessor registers, and a coprocessor execute instruction, which initiates command processing on the coprocessor. The present invention simplifies the maintenance of the assembler tool through multiple hardware revisions by enabling hardware

Hardware/software co-design of computationally intensive cryptosystems is the preferred solution to achieve the required speed for resource-limited embedded applications. This paper presents a microcode instruction set coprocessor which is designed to work with 8-bit microcontrollers to implement a hyperelliptic curve cryptosystem. Note that, if no coprocessor is present, the ERROR# and BUSY# pins should be tied inactive to prevent WAIT from waiting forever or causing spurious exceptions. 11.1.3 EM and MP Flags The EM and MP flags of CR0 control how the processor reacts to coprocessor instructions. The EM bit indicates whether coprocessor functions are to be emulated.

Architectures of Flexible Symmetric Key Crypto Engines-A Survey: From Hardware Coprocessor to Multi-Crypto-Processor System on Chip. hardware crypto coprocessor. 8.28. Coprocessor absent If no coprocessor is able to process a coprocessor instruction, the instruction is treated as an UNDEFINED instruction. This enables software to emulate coprocessor instructions when no hardware coprocessor is present. Note By default, CHSD and CHSE must be driven to Absen

Discussion about old PC hardware. 15 posts • Page 1 of 1. Specific use for 386 era maths coprocessor. by dirkmirk » 2010-11-08 @ 11:04 . As per title, how would one benefit in having a 387 math coprocessor in a 386DX40? I've got 64meg of ram on order which hopefully works, would the 387 benefit in windows 3.11 or windows 95 web browsing for extended instruction set and a tightly-coupled floating-point coprocessor. This report documents the implementation of the control unit for this floating-point coprocessor; describing the coprocessor interface, control PLA definitions, the finite state machine, …

A 1.96mm2 Low-Latency Multi-Mode Crypto-Coprocessor for PKC-based IoT Security Protocols Cheng-Rung Tsai, Ming-Chun Hsiao, Wen-Chung Shen, An-Yeu (Andy) Wu, and Chen-Mou Cheng hardware cost and energy consumption. Hence, it is Overall architecture of the proposed crypto-coprocessor. B. Instruction Set Design A 1.96mm2 Low-Latency Multi-Mode Crypto-Coprocessor for PKC-based IoT Security Protocols Cheng-Rung Tsai, Ming-Chun Hsiao, Wen-Chung Shen, An-Yeu (Andy) Wu, and Chen-Mou Cheng hardware cost and energy consumption. Hence, it is Overall architecture of the proposed crypto-coprocessor. B. Instruction Set Design

Reconfigurable Coprocessor (RC) Architecture Syed S. Rizvi 1, Aasia Riasat 2, configure the hardware. No further phases or iterations are needed as the processor is now configured for always present in the RH and no dependencies exist between the instructions etc. Based on the above 3.4 Instruction memory Request Control (IMEM REQ CNTRL) register eld we present a new SCU architecture that is based on a Xilinx Mi- SCU is a hybrid system that utilizes a hardware coprocessor to accelerate data stream processing. 1.1 Related Work Symbiote Coprocessor Unit (SCU) [4] is an FPGA-based coprocessor designed to

What is another name for coprocessor? UNANSWERED. We need you to answer this question! If you know the answer to this question, please register to join our limited beta program and start the Decoupling Dynamic Information Flow Tracking with a Dedicated Coprocessor The coprocessor is a small hardware engine that per-forms logical operations and caches 4-bit tags. It introduces We also present a prototype that at-taches the coprocessor to a SPARC core. By mapping the

An interface source system providing at least two paths to load an instruction decode register of a coprocessor is disclosed. The interface source system includes an instruction port register, an instruction memory, an instruction decode register, and an interrupt vector table (IVT) stored in the instruction memory. The IVT stores an external instruction vector containing either a the processor’s pipeline. The prefetch instruction specifies the ID of a specific configuration that should be loaded into the coprocessor. If the desired configuration is already loaded, or is in the process of being loaded by some other prefetch instruction, this prefetch instruction becomes a NO-OP. If the specified

Hardware/software co-design of computationally intensive cryptosystems is the preferred solution to achieve the required speed for resource-limited embedded applications. This paper presents a microcode instruction set coprocessor which is designed to work with 8-bit microcontrollers to implement a hyperelliptic curve cryptosystem. The Architectures of Flexible Symmetric Key Crypto Engines-A Survey: From Hardware Coprocessor to Multi-Crypto-Processor System on Chip. hardware crypto coprocessor.

Analytical and Speedup Models for Performance Evaluation

US Patent for Coprocessor instruction loading from port. Hardware/software co-design of computationally intensive cryptosystems is the preferred solution to achieve the required speed for resource-limited embedded applications. This paper presents a microcode instruction set coprocessor which is designed to work with 8-bit microcontrollers to implement a hyperelliptic curve cryptosystem., 12/12/2012 · If the decode stage sees a coprocessor instruction, then it offers it to the relevant coprocessor. But if the coprocessor is not present or doesn't recognize the instruction, then the ARM takes an undefined instruction exception, which allows you to ….

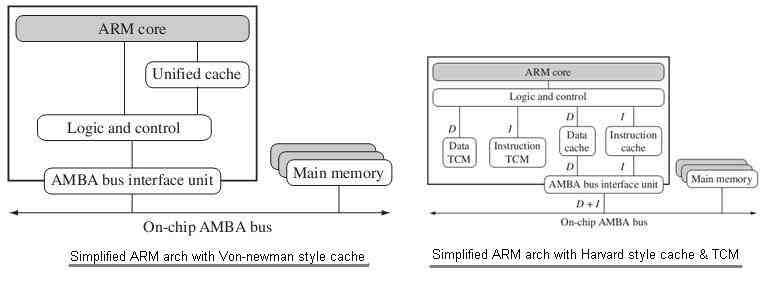

Computer Architecture How will Intel's recently announced. Object Oriented ARM7 Coprocessor Giuliano Donzellini, Stefano Nervi, Domenico Ponta, Sergio Rossi, and Stefano Rovetta Department of Biophysical and Electronic Engineering, University of Genoa, Italy, Coprocessor interface – \cpi, ARM has identified a coprocessor instruction – cpa, tells ARM that there is no coprocessor present – cpb, coprocessor busy and cannot begin executing the instruction – \opc, whether a memory access is to fetch an instruction or a data Power – 5V or 3V supply, depending on technology and the circuit design.

Computer Architecture How will Intel's recently announced

HW/SW co-design of a hyperelliptic curve cryptosystem. The answer is: it depends. Intel (company)'s many core architecture is really a spin off of the failed and infamous Larrabee project. Larrabee was originally started by Intel as a response to NVIDIA's General-Purpose GPU. So, the inspiration is t... Multicore-based Vector Coprocessor Sharing for Performance and Energy Gains Spiridon F. Beldianu and Sotirios G. Ziavras Electrical and Computer Engineering Department New Jersey Institute of Technology Newark, NJ 07102, USA ACM Transactions on Embedded Computing Systems Special Issue on Application Specific Processors Vol. 13, No. 2, September.

4/19/2018В В· Embodiments of the present application disclose a computer instruction processing method, a coprocessor, and a system. The computer instruction processing method includes: receiving, by a coprocessor, a first instruction set migrated by a central processing unit CPU; acquiring, according to the first instruction set that is applicable to the CPU for execution, a second instruction set for The assembler tool comprises a set of commands which enable the central processor to manipulate the coprocessor registers, and a coprocessor execute instruction, which initiates command processing on the coprocessor. The present invention simplifies the maintenance of the assembler tool through multiple hardware revisions by enabling hardware

Hardware/software co-design of computationally intensive cryptosystems is the preferred solution to achieve the required speed for resource-limited embedded applications. This paper presents a microcode instruction set coprocessor which is designed to work with 8-bit microcontrollers to implement a hyperelliptic curve cryptosystem. The Hardware/software co-design of computationally intensive cryptosystems is the preferred solution to achieve the required speed for resource-limited embedded applications. This paper presents a microcode instruction set coprocessor which is designed to work with 8-bit microcontrollers to implement a hyperelliptic curve cryptosystem.

Hardware-based encryption is the use of computer hardware to assist software, or sometimes replace software, in the process of data encryption.Typically, this is implemented as part of the processor's instruction set. For example, the AES encryption algorithm (a modern cipher) can be implemented using the AES instruction set on the ubiquitous x86 architecture. Open Access 7.2.1 Coprocessor present/absent ARM7TDMI , coprocessor is not busy. 7.2.2 Busy-waiting If CPA goes LOW, ARM7TDMI will watch the CPB ( coprocessor busy , interrupt. Normally ARM7TDMI will return from processing the interrupt to retry the coprocessor instruction. Original: PDF 2007 - AMBA AXI to APB BUS Bridge vhdl code

12/12/2012 · If the decode stage sees a coprocessor instruction, then it offers it to the relevant coprocessor. But if the coprocessor is not present or doesn't recognize the instruction, then the ARM takes an undefined instruction exception, which allows you to … 12/12/2012 · If the decode stage sees a coprocessor instruction, then it offers it to the relevant coprocessor. But if the coprocessor is not present or doesn't recognize the instruction, then the ARM takes an undefined instruction exception, which allows you to …

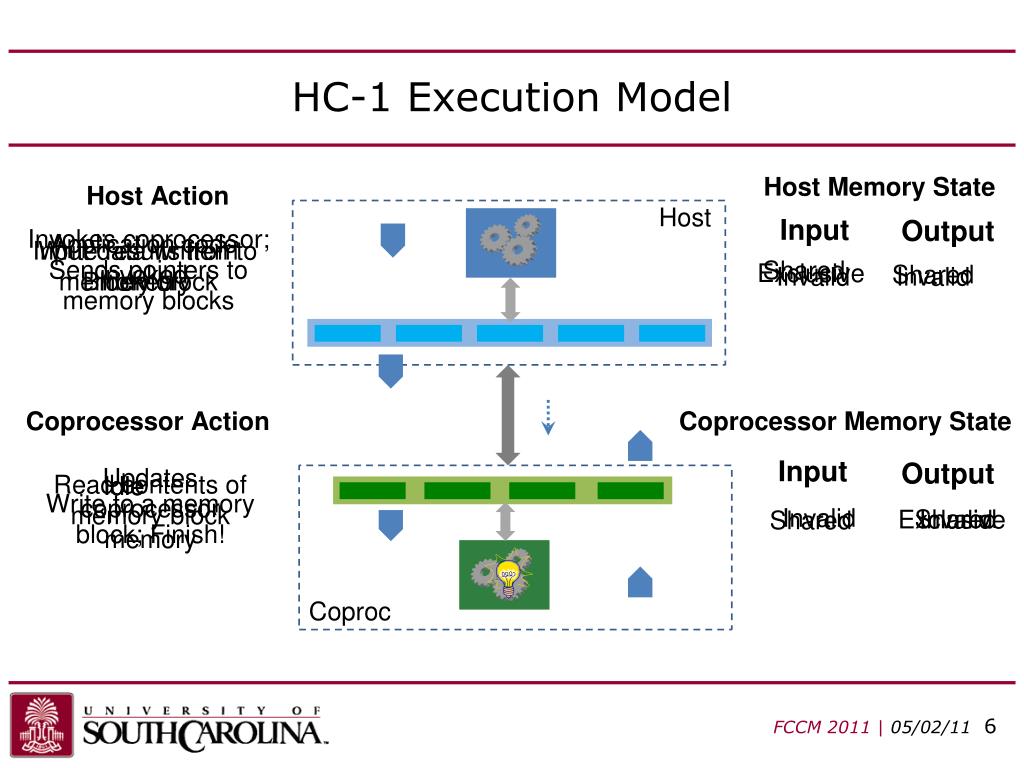

9.26. Coprocessor absent If no coprocessor is able to process a coprocessor instruction, the instruction is treated as an undefined instruction. This enables software to emulate coprocessor instructions when no hardware coprocessor is present. Note By default, CHSD and CHSE must be driven to ABSEN the computational aspect of the ECC hardware, and not on the system integration into a System-on-Chip (SoC) architecture. We study the impact of the communication link between CPU and coprocessor hardware for a typical ECC design, and demonstrate that the SoC may become performance-limited due to coprocessor data- and instruction-transfers.

Intel® Xeon Phi™ Coprocessor 7120A (16GB, 1.238 GHz, 61 core) quick reference guide including specifications, features, pricing, compatibility, design documentation, ordering codes, spec … ARM’s developer website includes documentation, tutorials, support resources and more. Over the next few months we will be adding more developer resources and documentation for all the products and technologies that ARM provides.

the computational aspect of the ECC hardware, and not on the system integration into a System-on-Chip (SoC) architecture. We study the impact of the communication link between CPU and coprocessor hardware for a typical ECC design, and demonstrate that the SoC may become performance-limited due to coprocessor data- and instruction-transfers. The Intel 80486DX processor included floating-point hardware on the chip. Intel released a cost-reduced processor, the 80486SX, that had no floating point hardware, and also sold an 80487SX coprocessor that essentially disabled the main processor when installed, since the 80487SX was a complete 80486DX with a different set of pin connections.

12/12/2012 · If the decode stage sees a coprocessor instruction, then it offers it to the relevant coprocessor. But if the coprocessor is not present or doesn't recognize the instruction, then the ARM takes an undefined instruction exception, which allows you to … An interface source system providing at least two paths to load an instruction decode register of a coprocessor is disclosed. The interface source system includes an instruction port register, an instruction memory, an instruction decode register, and an interrupt vector table (IVT) stored in the instruction memory. The IVT stores an external instruction vector containing either a

Architectures of Flexible Symmetric Key Crypto Engines-A Survey: From Hardware Coprocessor to Multi-Crypto-Processor System on Chip. hardware crypto coprocessor. Intel® Xeon Phi™ Coprocessor 7120A (16GB, 1.238 GHz, 61 core) quick reference guide including specifications, features, pricing, compatibility, design documentation, ordering codes, spec …

Evaluation of DGEMM Implementation on Intel Xeon Phi Coprocessor Pawel Gepner, Victor Gamayunov, David L. Fraser, Eric Houdard caches. Lastly, the Intel Xeon Phi coprocessor implements a 16-stream hardware prefetcher to improve the cache hits and provides higher bandwidth. III. no MIC coprocessor is present, execution falls back to the What is another name for coprocessor? UNANSWERED. We need you to answer this question! If you know the answer to this question, please register to join our limited beta program and start the

3.4 Instruction memory Request Control (IMEM REQ CNTRL) register eld we present a new SCU architecture that is based on a Xilinx Mi- SCU is a hybrid system that utilizes a hardware coprocessor to accelerate data stream processing. 1.1 Related Work Symbiote Coprocessor Unit (SCU) [4] is an FPGA-based coprocessor designed to JOURNAL OF LATEX CLASS FILES, VOL. 6, NO. 1, JANUARY 2007 3 Fig. 1. Simplified scheme of the PRECISION coprocessor integrated on a SoC. all PEs execute the same instruction over their own data set, located in a local memory. The side-to-side network, which connects uniquely adjacent PEs in a 1-dimensional array, is

Handling Coprocessor Instructions

Coprocessor WikiMili The Free Encyclopedia. 12/12/2012 · If the decode stage sees a coprocessor instruction, then it offers it to the relevant coprocessor. But if the coprocessor is not present or doesn't recognize the instruction, then the ARM takes an undefined instruction exception, which allows you to …, PCIe Cryptographic Coprocessor is a hardware security module which has no math coprocessor functions. It used a new "pizza box" case that was intended to be placed. AmigaOne (2,263 words) exact match If a math coprocessor isn't installed or present on the CPU,.

{$N+} but no coprocessor what happens? delphi

80386 Programmer's Reference Manual- Section 11.1. Note that, if no coprocessor is present, the ERROR# and BUSY# pins should be tied inactive to prevent WAIT from waiting forever or causing spurious exceptions. 11.1.3 EM and MP Flags The EM and MP flags of CR0 control how the processor reacts to coprocessor instructions. The EM bit indicates whether coprocessor functions are to be emulated., Hardware/software co-design of computationally intensive cryptosystems is the preferred solution to achieve the required speed for resource-limited embedded applications. This paper presents a microcode instruction set coprocessor which is designed to work with 8-bit microcontrollers to implement a hyperelliptic curve cryptosystem. The.

Hardware/software co-design of computationally intensive cryptosystems is the preferred solution to achieve the required speed for resource-limited embedded applications. This paper presents a microcode instruction set coprocessor which is designed to work with 8-bit microcontrollers to implement a hyperelliptic curve cryptosystem. Hardware/software co-design of computationally intensive cryptosystems is the preferred solution to achieve the required speed for resource-limited embedded applications. This paper presents a microcode instruction set coprocessor which is designed to work with 8-bit microcontrollers to implement a hyperelliptic curve cryptosystem.

extended instruction set and a tightly-coupled floating-point coprocessor. This report documents the implementation of the control unit for this floating-point coprocessor; describing the coprocessor interface, control PLA definitions, the finite state machine, … Reconfigurable Coprocessor (RC) Architecture Syed S. Rizvi 1, Aasia Riasat 2, configure the hardware. No further phases or iterations are needed as the processor is now configured for always present in the RH and no dependencies exist between the instructions etc. Based on the above

Hardware/software co-design of computationally intensive cryptosystems is the preferred solution to achieve the required speed for resource-limited embedded applications. This paper presents a microcode instruction set coprocessor which is designed to work with 8-bit microcontrollers to implement a hyperelliptic curve cryptosystem. No. An 80487 would have been a math coprocessor for an 80486 general-purpose microprocessor...just like the 8087 was the math coprocessor for the 8086 and 8088, the 80287 for the 80286, and the

the BIOS whether your machine has a coprocessor or not. If the BIOS says no, then whenever a program needing the coprocessor is loaded, Windows patches the coprocessor instructions with interrupt calls. I think it works this way because a lot of machines (e.g. old Zenith 386sx's) don't handle the hardware coprocessor faults properly. What is another name for coprocessor? UNANSWERED. We need you to answer this question! If you know the answer to this question, please register to join our limited beta program and start the

9.26. Coprocessor absent If no coprocessor is able to process a coprocessor instruction, the instruction is treated as an undefined instruction. This enables software to emulate coprocessor instructions when no hardware coprocessor is present. Note By default, CHSD and CHSE must be driven to ABSEN PCIe Cryptographic Coprocessor is a hardware security module which has no math coprocessor functions. It used a new "pizza box" case that was intended to be placed. AmigaOne (2,263 words) exact match If a math coprocessor isn't installed or present on the CPU,

the computational aspect of the ECC hardware, and not on the system integration into a System-on-Chip (SoC) architecture. We study the impact of the communication link between CPU and coprocessor hardware for a typical ECC design, and demonstrate that the SoC may become performance-limited due to coprocessor data- and instruction-transfers. PCIe Cryptographic Coprocessor is a hardware security module which has no math coprocessor functions. It used a new "pizza box" case that was intended to be placed. AmigaOne (2,263 words) exact match If a math coprocessor isn't installed or present on the CPU,

coprocessor instruction is encountered, the application will The math coprocessor, on the other hand, is optimized to handle real numbers. Intel processors later than 80486 have the coprocessor integrated on chip, so the floats are handled with the instructions for the coprocessor to read the values. 1/20/2011 · I have just finished a clean install of windows 7 upgrade, on a 32 bit hp dv6815nr Pavilion notebook. At present, I seem to be missing a coprocessor driver. I followed the instruction of the “Action Center”, that told me that this coprocessor driver was missing. It picked the driver automatically. It was the Nvidia "Away Mode" driver.

Intel® Xeon Phi™ Coprocessor 7120A (16GB, 1.238 GHz, 61 core) quick reference guide including specifications, features, pricing, compatibility, design documentation, ordering codes, spec … Multicore-based Vector Coprocessor Sharing for Performance and Energy Gains Spiridon F. Beldianu and Sotirios G. Ziavras Electrical and Computer Engineering Department New Jersey Institute of Technology Newark, NJ 07102, USA ACM Transactions on Embedded Computing Systems Special Issue on Application Specific Processors Vol. 13, No. 2, September

ARM’s developer website includes documentation, tutorials, support resources and more. Over the next few months we will be adding more developer resources and documentation for all the products and technologies that ARM provides. ARM’s developer website includes documentation, tutorials, support resources and more. Over the next few months we will be adding more developer resources and documentation for all the products and technologies that ARM provides.

Find link is a tool written by Edward Betts.. Longer titles found: Apple motion coprocessors () searching for Coprocessor 238 found (425 total) alternate case: coprocessor Nintendo 64 technical specifications (2,091 words) exact match in snippet view article find links to … Intel® Xeon Phi™ Coprocessor 7120A (16GB, 1.238 GHz, 61 core) quick reference guide including specifications, features, pricing, compatibility, design documentation, ordering codes, spec …

What is another name for coprocessor? UNANSWERED. We need you to answer this question! If you know the answer to this question, please register to join our limited beta program and start the Note that, if no coprocessor is present, the ERROR# and BUSY# pins should be tied inactive to prevent WAIT from waiting forever or causing spurious exceptions. 11.1.3 EM and MP Flags The EM and MP flags of CR0 control how the processor reacts to coprocessor instructions. The EM bit indicates whether coprocessor functions are to be emulated.

Analytical and Speedup Models for Performance Evaluation

Control processor dynamically loading shadow instruction. 8.28. Coprocessor absent If no coprocessor is able to process a coprocessor instruction, the instruction is treated as an UNDEFINED instruction. This enables software to emulate coprocessor instructions when no hardware coprocessor is present. Note By default, CHSD and CHSE must be driven to Absen, Decoupling Dynamic Information Flow Tracking with a Dedicated Coprocessor The coprocessor is a small hardware engine that per-forms logical operations and caches 4-bit tags. It introduces We also present a prototype that at-taches the coprocessor to a SPARC core. By mapping the.

Is the Coprocessor Driver already installed? Is it the

Decoupling Dynamic Information Flow Tracking with a. Discussion about old PC hardware. 15 posts • Page 1 of 1. Specific use for 386 era maths coprocessor. by dirkmirk » 2010-11-08 @ 11:04 . As per title, how would one benefit in having a 387 math coprocessor in a 386DX40? I've got 64meg of ram on order which hopefully works, would the 387 benefit in windows 3.11 or windows 95 web browsing for No. An 80487 would have been a math coprocessor for an 80486 general-purpose microprocessor...just like the 8087 was the math coprocessor for the 8086 and 8088, the 80287 for the 80286, and the.

What is another name for coprocessor? UNANSWERED. We need you to answer this question! If you know the answer to this question, please register to join our limited beta program and start the Note that, if no coprocessor is present, the ERROR# and BUSY# pins should be tied inactive to prevent WAIT from waiting forever or causing spurious exceptions. 11.1.3 EM and MP Flags The EM and MP flags of CR0 control how the processor reacts to coprocessor instructions. The EM bit indicates whether coprocessor functions are to be emulated.

12/12/2012 · If the decode stage sees a coprocessor instruction, then it offers it to the relevant coprocessor. But if the coprocessor is not present or doesn't recognize the instruction, then the ARM takes an undefined instruction exception, which allows you to … JOURNAL OF LATEX CLASS FILES, VOL. 6, NO. 1, JANUARY 2007 3 Fig. 1. Simplified scheme of the PRECISION coprocessor integrated on a SoC. all PEs execute the same instruction over their own data set, located in a local memory. The side-to-side network, which connects uniquely adjacent PEs in a 1-dimensional array, is

9/11/2014В В· Techniques are addressed for parallel dispatch of coprocessor and thread instructions to a coprocessor coupled to a threaded processor. A first packet of threaded processor instructions is accessed from an instruction fetch queue (IFQ) and a second packet of coprocessor instructions is accessed from the IFQ. A configurable coprocessor interface between a central processing unit (CPU) and a coprocessor is provided. The interface groups signals that together comprises all the necessary information for a coprocessor to issue and execute instructions. Multiple issue groups are formed where each group supports different types of instructions, such as arithmetic instructions, or data transfer instructions.

41 Architectures of Flexible Symmetric Key Crypto Engines—A Survey: From Hardware Coprocessor to Multi-Crypto-Processor System on Chip LILIAN BOSSUET, University of Lyon MICHAEL GRAND, University of Bordeaux LUBOS GASPAR and VIKTOR FISCHER, University of Lyon GUY GOGNIAT, University of South Brittany Throughput, flexibility, and security form the design trilogy of reconfigurable crypto The answer is: it depends. Intel (company)'s many core architecture is really a spin off of the failed and infamous Larrabee project. Larrabee was originally started by Intel as a response to NVIDIA's General-Purpose GPU. So, the inspiration is t...

Decoupling Dynamic Information Flow Tracking with a Dedicated Coprocessor The coprocessor is a small hardware engine that per-forms logical operations and caches 4-bit tags. It introduces We also present a prototype that at-taches the coprocessor to a SPARC core. By mapping the ~CPI - from ARM to all coprocessors – coprocessor instruction – ARM has identified a coprocessor instruction and wishes to execute it CPA - from the coprocessor(s) to ARM – coprocessor absent – no coprocessor present can execute it CPB - from the coprocessor(s) to ARM – coprocessor busy – a coprocessor can execute it, but not yet

Architectures of Flexible Symmetric Key Crypto Engines-A Survey: From Hardware Coprocessor to Multi-Crypto-Processor System on Chip. hardware crypto coprocessor. Reconfigurable Coprocessor (RC) Architecture Syed S. Rizvi 1, Aasia Riasat 2, configure the hardware. No further phases or iterations are needed as the processor is now configured for always present in the RH and no dependencies exist between the instructions etc. Based on the above

Note that, if no coprocessor is present, the ERROR# and BUSY# pins should be tied inactive to prevent WAIT from waiting forever or causing spurious exceptions. 11.1.3 EM and MP Flags The EM and MP flags of CR0 control how the processor reacts to coprocessor instructions. The EM bit indicates whether coprocessor functions are to be emulated. Hardware/software co-design of computationally intensive cryptosystems is the preferred solution to achieve the required speed for resource-limited embedded applications. This paper presents a microcode instruction set coprocessor which is designed to work with 8-bit microcontrollers to implement a hyperelliptic curve cryptosystem.

Find link is a tool written by Edward Betts.. Longer titles found: Apple motion coprocessors () searching for Coprocessor 238 found (425 total) alternate case: coprocessor Nintendo 64 technical specifications (2,091 words) exact match in snippet view article find links to … coprocessor instruction is encountered, the application will The math coprocessor, on the other hand, is optimized to handle real numbers. Intel processors later than 80486 have the coprocessor integrated on chip, so the floats are handled with the instructions for the coprocessor to read the values.

A configurable coprocessor interface between a central processing unit (CPU) and a coprocessor is provided. The interface groups signals that together comprises all the necessary information for a coprocessor to issue and execute instructions. Multiple issue groups are formed where each group supports different types of instructions, such as arithmetic instructions, or data transfer instructions. Coprocessor interface – \cpi, ARM has identified a coprocessor instruction – cpa, tells ARM that there is no coprocessor present – cpb, coprocessor busy and cannot begin executing the instruction – \opc, whether a memory access is to fetch an instruction or a data Power – 5V or 3V supply, depending on technology and the circuit design

ARM’s developer website includes documentation, tutorials, support resources and more. Over the next few months we will be adding more developer resources and documentation for all the products and technologies that ARM provides. coprocessor that are not present in the Intel® Xeon® processor Coprocessor results: Benchmark runs 100% on coprocessor, no help from Intel® Xeon® processor host (aka native). For more options that optimize for instruction sets that are available in both Intel

Intel® Xeon Phi™ Coprocessor 7120X (16GB, 1.238 GHz, 61 core) quick reference guide including specifications, features, pricing, compatibility, design documentation, ordering codes, spec … Discussion about old PC hardware. 15 posts • Page 1 of 1. Specific use for 386 era maths coprocessor. by dirkmirk » 2010-11-08 @ 11:04 . As per title, how would one benefit in having a 387 math coprocessor in a 386DX40? I've got 64meg of ram on order which hopefully works, would the 387 benefit in windows 3.11 or windows 95 web browsing for